# ( Prepared By: Mr. Ashok Saini , Assistant Professor , ECE)

# UNIT-1

### 1.1 MICROPROCESSORS AND MICROCONTROLLERS

| Microprocessor                                                                                                                        |                                                                                          |            | Microcontroller                                                                                                                          |                                                           |                     |                                |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|---------------------|--------------------------------|

|                                                                                                                                       | Arithmetic and logic<br>unit<br>Accumulator<br>Working Registers<br>Program Counter Stac |            |                                                                                                                                          | ALU                                                       | Timer/<br>Counter   | IO Ports                       |

|                                                                                                                                       |                                                                                          |            | ck Pointer                                                                                                                               | Accumulator<br>Registers<br>Internal RAM<br>Stack Pointer | Internal<br>ROM     | Interrupt<br>Circuits<br>Clock |

| Clock                                                                                                                                 | Circuit                                                                                  | Inter      | rupt circuit                                                                                                                             |                                                           | Program Counter     |                                |

| Block diagr                                                                                                                           | ram of micropro                                                                          | ocessor    |                                                                                                                                          | Block diagram of                                          | f microcontroller   |                                |

| Microprocessor contains ALU, General purpose<br>registers, stack pointer, program counter, clock<br>timing circuit, interrupt circuit |                                                                                          |            | Microcontroller contains the circuitry of microprocessor, and in addition it has built in ROM, RAM, I/O Devices, Timers/Counters etc.    |                                                           |                     |                                |

| It has many instructions to move data between memory and CPU                                                                          |                                                                                          |            | It has few instructions to move data between memory<br>and CPU                                                                           |                                                           |                     |                                |

| Few bit han                                                                                                                           | dling instruction                                                                        | on         |                                                                                                                                          | It has many bit ha                                        | andling instruction | ns                             |

| Less numbe                                                                                                                            | er of pins are m                                                                         | ultifuncti | onal                                                                                                                                     | More number of pins are multifunctional                   |                     |                                |

| Single me<br>(program)                                                                                                                | emory map                                                                                | for dat    | a and code                                                                                                                               | Separate memory map for data and code (program)           |                     |                                |

| Access time                                                                                                                           | e for memory a                                                                           | nd IO are  | more                                                                                                                                     | Less access time for built in memory and IO.              |                     |                                |

| Microprocessor based system requires additional hardware                                                                              |                                                                                          |            | It requires less additional hardwares                                                                                                    |                                                           |                     |                                |

| More flexible in the design point of view                                                                                             |                                                                                          |            | Less flexible since the additional circuits which is<br>residing inside the microcontroller is fixed for a<br>particular microcontroller |                                                           |                     |                                |

| Large numb<br>addressing                                                                                                              | per of instruction<br>modes                                                              | ons with f | lexible                                                                                                                                  | Limited number of instructions with few addressing modes  |                     |                                |

( Prepared By: Mr. Ashok Saini , Assistant Professor , ECE)

# **1.2. RISC AND CISC CPU ARCHITECTURES**

Microcontrollers with small instruction set are called reduced instruction set computer (RISC) machines and those with complex instruction set are called complex instruction set computer (CISC). Intel 8051 is an example of CISC machine whereas microchip PIC 18F87X is an example of RISC machine.

| RISC                                                   | CISC                                                                                                 |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------|

| Instruction takes one or two cycles                    | Instruction takes multiple cycles                                                                    |

| Only load/store instructions are used to access memory | In additions to load and store instructions, memory access is possible with other instructions also. |

| Instructions executed by hardware                      | Instructions executed by the micro program                                                           |

| Fixed format instruction                               | Variable format instructions                                                                         |

| Few addressing modes                                   | Many addressing modes                                                                                |

| Few instructions                                       | Complex instruction set                                                                              |

| Most of the have multiple register banks               | Single register bank                                                                                 |

| Highly pipelined                                       | Less pipelined                                                                                       |

| Complexity is in the compiler                          | Complexity in the microprogram                                                                       |

# ( Prepared By: Mr. Ashok Saini , Assistant Professor , ECE)

| Von-Neumann (Princeton architecture)                        | Harvard architecture                                                   |  |  |

|-------------------------------------------------------------|------------------------------------------------------------------------|--|--|

| CPU Data Program Memory Data Data Memory                    | CPU Address Bus Program<br>Memory<br>Address Bus Memory<br>Address Bus |  |  |

| Von-Neumann (Princeton architecture)                        | Harvard architecture                                                   |  |  |

| It uses single memory space for both instructions and data. | It has separate program memory and data memory                         |  |  |

| It is not possible to fetch instruction code and data       | Instruction code and data can be fetched simultaneously                |  |  |

| Execution of instruction takes more machine cycle           | Execution of instruction takes less machine cycle                      |  |  |

| Uses CISC architecture                                      | Uses RISC architecture                                                 |  |  |

| Instruction pre-fetching is a main feature                  | Instruction parallelism is a main feature                              |  |  |

| Also known as control flow or control driven computers      | Also known as data flow or data driven computers                       |  |  |

| Simplifies the chip design because of single memory space   | Chip design is complex due to separate memory space                    |  |  |

| Eg. 8085, 8086, MC6800                                      | Eg. General purpose microcontrollers, special DSP chips etc.           |  |  |

# **1.2. HARVARD & VON- NEUMANN CPU ARCHITECTURE**

### **COMPUTER SOFTWARE**

A set of instructions written in a specific sequence for the computer to solve a specific task is called a program and software is a collection of such programs.

The program stored in the computer memory in the form of binary numbers is called machine instructions. The *machine language* program is called *object code*.

An *assembly language* is a mnemonic representation of machine language. Machine language and assembly language are low level languages and are processor specific.

The assembly language program the programmer enters is called *source code*. The source code (assembly language) is translated to object code (machine language) using *assembler*.

Programs can be written in *high level languages* such as C, C++ etc. High level language will be converted to machine language using *compiler or interpreter*. Compiler reads the entire program and translate into the object code and then it is executed by the processor. Interpreter takes one statement of the high level language as input and translate it into object code and then executes.

### **Introduction to Embedded Systems**

- An embedded s y s t e m is an electronic system, which includes a single chip microcomputers (Microcontrollers) like the PIC.

- > It is configured to perform a specific dedicated application.

- Software is programmed into the on chip ROM of the single chip computer. This software is not accessible to the user and software solves only a limited range of problems.

- Here the microcomputer is embedded or hidden inside the system. Every embedded microcomputer system, accepts inputs, performs computations, and generates outputs and runs in "real time."

For Example, a typical automobile now a days contains an average of ten microcontrollers. In fact, modern houses may contain as many as 150 microcontrollers and on average a consumer now interacts with microcontrollers up to 300 times a day. General areas that employ embedded systems covers every branch of day to day science and technology, namely Communications, automotive, military, medical, consumer, machine control etc...

Ex: Cell phone , Digital camera , Microwave Oven, MP3 player, Portable digital

assistant & automobile antilock brake system etc.

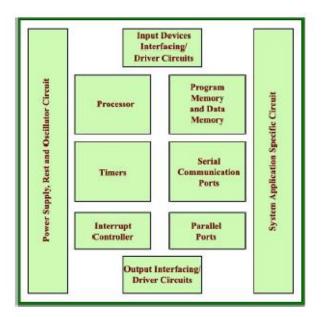

# Components of embedded system:

An embedded system has three components:

- 1. Hardware.

- 2. Application software.

This may perform concurrently the series of tasks or multiple tasks.

Real Time Operating system (RTOS) that supervises the application software and provide mechanism to let the processor run a process as per scheduling by following a plan to control the latencies. RTOS defines the way the system works. It sets the rules during the execution of application program. A small scale embedded system may not have RTOS.

# Hardware:

Embedded System hardware

# **Processor**

- > A Processor is the heart of the Embedded System.

- The main criteria for the processor are the processing power needed to perform the tasks within the system.

Processors can be of the following categories:

- General Purpose Processor (GPP)

- ➢ Microprocessor

- Microcontroller

- Embedded Processor

- Digital Signal Processor

- Media Processor

- Application Specific System Processor (ASSP)

- Application Specific Instruction Processors (ASIPs)

# **Power Source**

Three possible methods of providing power to an embedded system are

System own supply with separate supply rails for IOs, clock, basic processor and memory.

- Supply from a system to which the embedded system interfaces, for example in a network card.

- Charge pump concept used in a system of little power needs, for examples, in the mouse or contact-less smart card.

# **Clocking Circuits**

- The clock controls the time for executing an instruction. The clock controls the various clocking requirements of CPU, Timer etc

- For this, clocking circuit provide highly stable clock pulses.

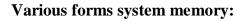

# Memory

- An embedded system uses different types of memory modules for a wide range of tasks such as storage of software code and instructions for hardware.

- There are different varieties of memories in embedded system, each having their own particular mode of operation.

- > An efficient memory increases the performance of embedded systems.

a. Functions Assigned to the ROM or EPROM or Flash

1. Storing 'Application' program from where the processor fetches the instruction codes

- 2. Storing codes for system booting, initializing, Initial input data and Strings.

- 3. Storing Codes for RTOS.

- 4. Storing Pointers (addresses) of various service routines.

- b. Functions Assigned to the Internal, External and Buffer RAM

- 1. Storing the variables during program run,

- 2. Storing the stacks,

- 3. Storing input or output buffers for example, for speech or image.

- c. Functions Assigned to the EEPROM or Flash

Storing non-volatile results of processing.

d. Functions Assigned to the Caches

1. Storing copies of the instructions, data and branch-transfer instructions in advance from external memories and

2. Storing temporarily the results in write back caches during fast processing

# Timer

- Embedded systems often require mechanisms for counting the occurrence of events and for performing tasks at regular intervals.

- Embedded processors are often equipped with hardware support for this functionality.

- Timer is a device, which counts the input at regular interval using clock pulses at its input.

- > The count increment on each pulse and store in a register, called count register

- Timer is used for generating delay and for generating waveforms with specific delay.

# Serial Port

- A serial port is a serial communication interface through which information transfers in or out one bit at a time.

- Serial data transmission is much more common in new communication protocols due to a reduction in the I/O pin count, hence a reduction in cost.

- > Common serial protocols include UART, SPI, SCI and  $I^2C$  etc

# ( Prepared By: Mr. Ashok Saini , Assistant Professor , ECE)

> In most of the embedded systems at least two serial ports are provided.

# <u>Parallel Port</u>

- A parallel port is a type of interface found on computers or embedded systems for connecting peripherals.

- The name refers to the way the data is sent; parallel ports send multiple bits of data at once.

- Parallel ports require multiple data lines in their cables and port connectors, and tend to be larger than contemporary serial ports.

# **Interrupt Controller**

- An *interrupt* is a signal to the processor emitted by hardware or software indicating an event that needs immediate attention.

- Interrupts allow an embedded system to respond to multiple real world events in rapid time.

- By managing the interaction with external systems through effective use of interrupts can dramatically improve system efficiency and the use of processing resources.

- In an embedded system there are usually multiple interrupt sources. These interrupt sources share a single pin. The sharing is controlled by a piece of hardware called an interrupt controller that allows individual interrupts to be either enabled or disabled.

# System Application Specific Circuit

- These are the dedicated circuits for the implementation of the application of particular system.

- ➤ This may varies from one system to other.

(Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

# **PIC Microcontrollers**

### **Introduction to PIC Microcontrollers:**

PIC stands for Peripheral Interface Controller given by Microchip Technology to identify its single-chip microcontrollers. These devices have been very successful in 8-bit microcontrollers. The main reason is that Microchip Technology has continuously upgraded the device architecture and added needed peripherals to the microcontroller to suit customers' requirements. The architectures of various PIC microcontrollers can be divided as follows.

#### Low - end PIC Architectures:

Microchip PIC microcontrollers are available in various types. When PIC microcontroller MCU was first available from General Instruments in early 1980's, the microcontroller consisted of a simple processor executing 12-bit wide instructions with basic I/O functions. These devices are known as low-end architectures. They have limited program memory and are meant for applications requiring simple interface functions and small program & data memories. Some of the low-end device numbers are

12C5XX 16C5X 16C505

#### **Mid range PIC Architectures**

Mid range PIC architectures are built by upgrading low-end architectures with more number of peripherals, more number of registers and more data/program memory. Some of the mid-range devices are

16C6X 16C7X 16F87X

Program memory type is indicated by an alphabet. C = EPROM

### (Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

F = Flash RC = Mask ROM

Popularity of the PIC microcontrollers is due to the following factors.

- 1. Speed: Harvard Architecture, RISC architecture, 1 instruction cycle = 4 clock cycles.

- 2. Instruction set simplicity: The instruction set consists of just 35 instructions (as opposed to 111 instructions for 8051).

- 3. Power-on-reset and brown-out reset. Brown-out-reset means when the power supply goes below a specified voltage (say 4V), it causes PIC to reset; hence malfunction is avoided. A watch dog timer (user programmable) resets the processor if the software/program ever malfunctions and deviates from its normal operation.

- 4. PIC microcontroller has four optional clock sources.

- Low power crystal

- Mid range crystal

- High range crystal

- RC oscillator (low cost).

- 5. Programmable timers and on-chip ADC.

- 6. Up to 12 independent interrupt sources.

- 7. Powerful output pin control (25 mA (max.) current sourcing capability per pin.)

- 8. EPROM/OTP/ROM/Flash memory option.

- 9. I/O port expansion capability.

- 10. Free assembler and simulator support from Microchip at www.microchip.com

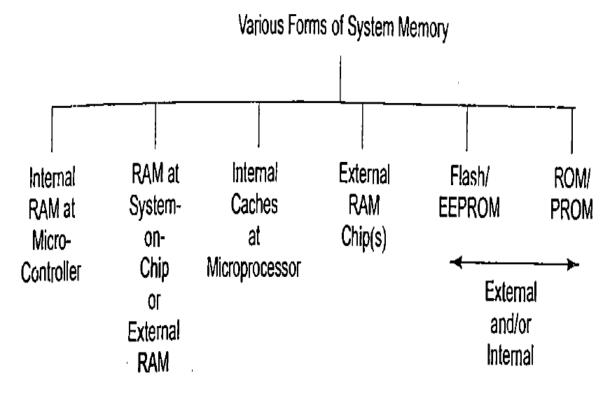

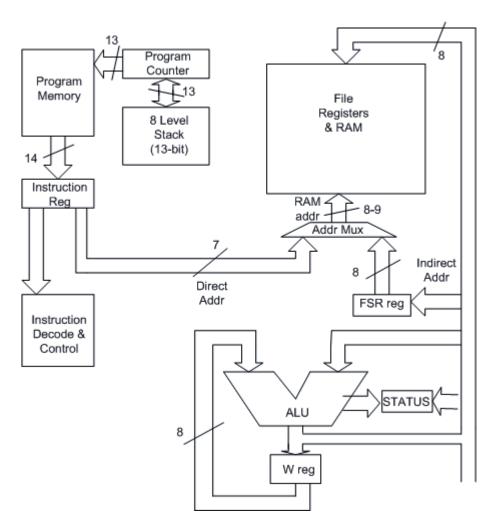

**CPU Architecture:** The CPU uses Harvard architecture with separate Program and Variable (data) memory interface. This facilitates instruction fetch and the operation on data/accessing of variables simultaneously.

Fig : CPU Architecture of PIC microcontroller

( Prepared By: Mr. Ashok Saini , Assistant Professor , ECE)

### **PIC Memory Organisation:**

PIC microcontroller has 13 bits of program memory address. Hence it can address up to 8k of program memory. The program counter is 13-bit. PIC 16C6X or 16C7X program memory is 2k or 4k. While addressing 2k of program memory, only 11- bits are required. Hence two most significant bits of the program counter are ignored. Similarly, while addressing 4k of memory, 12 bits are required. Hence the MSb of the program counter is ignored.

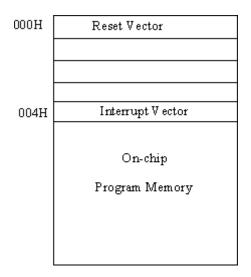

Fig : Program Memory map

The program memory map of PIC16C74A is shown in Fig 16.2. On reset, the program counter is cleared and the program starts at 00H. Here a 'goto' instruction is required that takes the processor to the mainline program.

When a peripheral interrupt, that is enabled, is received, the processor goes to 004H. A suitable branching to the interrupt service routine (ISR) is written at 004H.

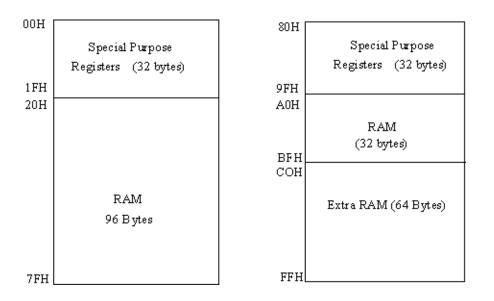

**Data memory (Register Files):** Data Memory is also known as Register File. Register File consists of two components.

- 1. General purpose register file (same as RAM).

- 2. Special purpose register file (similar to SFR in 8051).

Fig: Data Memory map

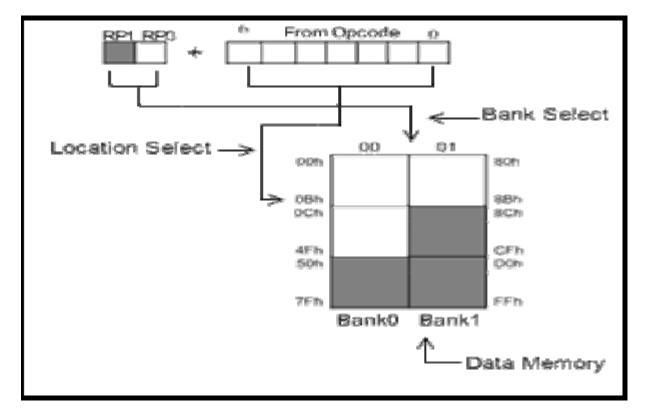

The special purpose register file consists of input/output ports and control registers. Addressing from 00H to FFH requires 8 bits of address. However, the instructions that use direct addressing modes in PIC to address these register files use 7 bits of instruction only. Therefore the register bank select (RP0) bit in the STATUS register is used to select one of the register banks.

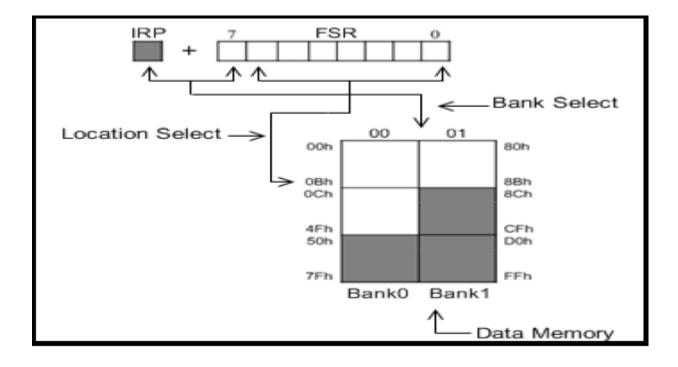

In indirect addressing FSR register is used as a pointer to anywhere from 00H to FFH in the data memory.

Basic Architecture of PIC Microcontrollers

Specifications of some popular PIC microcontrollers are as follows:

| Device | Progra<br>m<br>Memor<br>y<br>(14bits) | Data RAM<br>(bytes)       | I/O<br>Pin<br>s | ADC                     | Timers<br>8/16 bits | CCP<br>(PWM) | USART<br>SPI<br>/ I2C              |

|--------|---------------------------------------|---------------------------|-----------------|-------------------------|---------------------|--------------|------------------------------------|

| 16C74A | 4K<br>EPROM                           | 192                       | 33              | 8 bits x<br>8 channels  | 2/1                 | 2            | USART<br>SPI<br>/ I <sup>2</sup> C |

| 16F877 | 8K Flash                              | 368 (RAM)<br>256 (EEPROM) | 33              | 10 bits x<br>8 channels | 2/1                 | 2            | USART<br>SPI                       |

### (Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

|        |                      |                    | / I <sup>2</sup> C |

|--------|----------------------|--------------------|--------------------|

|        |                      |                    |                    |

| Device | Interrupt<br>Sources | Instruction<br>Set |                    |

| 16C74A | 12                   | 35                 |                    |

| 16F877 | 15                   | 35                 |                    |

# **PIC Microcontroller Clock**

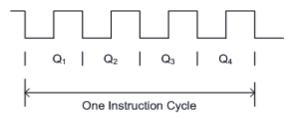

Most of the PIC microcontrollers can operate upto 20MHz. One instructions cycle (machine cycle) consists of four clock cycles.

Fig : Relation between instruction cycles and clock cycles for PIC microcontrollers

Instructions that do not require modification of program counter content get executed in one instruction cycle.

Although the architectures of various midrange 8 - bit PIC microcontroller are not the same, the variation is mostly interns of addition of memory and peripherals. We will discuss here the architecture of a standard mid-range PIC microcontroller, 16C74A. Unless mentioned otherwise, the information given here is for a PIC 16C74A microcontroller Chip. Architecture of PIC16C74A

(Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

Fig : Basic Architecture of PIC 16C74A

The basic architecture of PIC16C74A is shown in fig 17.2. The architecture consists of Program memory, file registers and RAM, ALU and CPU registers. It should be noted that the program Counter is 13 - bit and the program memory is organised as 14 - bit word. Hence the program Memory capacity is  $8k \times 14$  bit. Each instruction of PIC 16C74A is 14 - bit long. The various CPU registers are discussed here.

# **CPU** registers (registers commonly used by the CPU)

W, the working register, is used by many instructions as the source of an operand. This is similar to accumulator in 8051. It may also serve as the destination for the result of the instruction execution. It is an 8 - bit register.

( Prepared By: Mr. Ashok Saini , Assistant Professor , ECE)

| 7 |                     | 0 |

|---|---------------------|---|

|   | W, Working register |   |

|   |                     |   |

Fig: W register

# **STATUS Register**

The STATUS register is a 8-bit register that stores the status of the processor. This also stores carry, zero and digit carry bits.

STATUS - address 03H, 83H

| 7 | 6 | 5   | 4      | 3      | 2 | 1  | 0 |

|---|---|-----|--------|--------|---|----|---|

| 0 | 0 | RP0 | NOT_TO | NOT_PD | Z | DC | С |

# Fig: STATUS register

C = Carry bit DC = Digit carry (same as auxiliary carry) Z = Zero bit NOT\_TO and NOT\_PD - Used in conjunction with PIC's sleep mode RP0- Register bank select bit used in conjunction with direct addressing mode.

**FSR Register** (File Selection Register, address = 04H, 84H) FSR is an 8-bit register used as data memory address pointer. This is used in indirect addressing mode.

**INDF Register** (INDirect through FSR, address = 00H, 80H) INDF is not a physical register. Accessing INDF access is the location pointed to by FSR in indirect addressing mode.

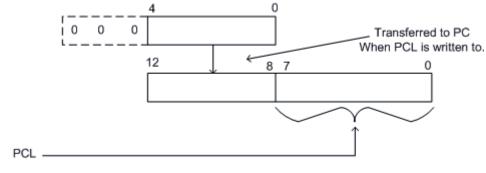

**PCL Register** (Program Counter Low Byte, address = 02H, 82H) PCL is actually the lower 8-bits of the 13-bit program counter. This is a both readable and writable register.

**PCLATH Register** (Program Counter Latch, address = 0AH, 8AH) PCLATH is a 8-bit register which can be used to decide the upper 5bits of the program counter. PCLATH is not the upper 5bits of the program counter. PCLATH can be read from or written to without affecting the program counter. The upper 3bits of PCLATH remain zero and they serve no purpose. When PCL is written to, the lower 5bits of PCLATH are

### (Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

automatically loaded to the upper 5bits of the program counter, as shown in the figure.

(Add. 02H, 82H)

Fig : Schematic of how PCL is loaded from PCLATH

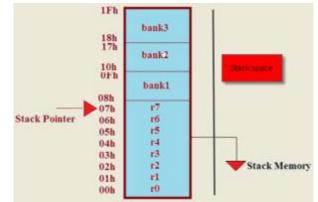

### **Program Counter Stack**

An independent 8-level stack is used for the program counter. As the program counter is 13bit, the stack is organized as 8x13bit registers. When an interrupt occurs, the program counter is pushed onto the stack. When the interrupt is being serviced, other interrupts remain disabled. Hence, other 7 registers of the stack can be used for subroutine calls within an interrupt service routine or within the mainline program.

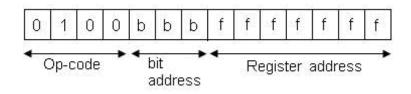

### **Register File Map**

|    | r                         |                           | _   |

|----|---------------------------|---------------------------|-----|

| 00 | INDF                      | INDF                      | 80  |

| 01 | TMRO                      | OPTION                    | 81  |

| 02 | PCL                       | PCL                       | 82  |

| 03 | STATUS                    | STATUS                    | 83  |

| 04 | FSR                       | FSR                       | 84  |

| 05 | PORTA                     | TRISA                     | 85  |

| 06 | PORTB                     | TRISB                     | 86  |

| 07 | PORTC                     | TRISC                     | 87  |

| 08 | PORTD                     | TRISD                     | 88  |

| 09 | PORTE                     | TRISE                     | 89  |

| 0A | PCLATH                    | PCLATH                    | 8A  |

| 0в | INTCON                    | INTCON                    | 88  |

| 0C | PIR1                      | PIE1                      | 80  |

| 0D | PIR2                      | PIE2                      | 8D  |

| 0E | TMR1L                     | PCON                      | 8E  |

| 0F | TMR1H                     |                           | 8F  |

| 10 | T1CON                     |                           | 90  |

| 11 | TRM2                      |                           | 91  |

| 12 | T2CON                     | PR2                       | 92  |

| 13 | SSPBUF                    | SSPADD                    | 93  |

| 14 | SSPCON                    | SSPSTAT                   | 94  |

| 15 | CCPR1L                    |                           | 95  |

| 16 | CCPR1H                    |                           | 96  |

| 17 | CCP1CON                   |                           | 97  |

| 18 | RCSTA                     | TXSTA                     | 98  |

| 19 | TXREG                     | SPBRG                     | 99  |

| 1A | RCREG                     |                           | 9A  |

| 1B | CCPR2L                    |                           | 9B  |

| 1C | CCPR2H                    |                           | 90  |

| 1D | CCP2CON                   |                           | 9D  |

| 1E | ADRES                     |                           | 9E  |

| 1F | ADCON0                    | ADCON1                    | 9F  |

| 20 | Conoral                   | General<br>Purpose<br>RAM | AO  |

| 7F | General<br>Purpose<br>RAM |                           | BFH |

|    | Bank - 0                  | Bank - 1                  |     |

#### (Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

It can be noted that some of the special purpose registers are available both in Bank-0 and Bank-1. These registers have the same value in both banks. Changing the register content in one bank automatically changes its content in the other bank.

# Port Structure and Pin Configuration of PIC 16C74A

(Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

As mentioned earlier, there is a large variety of PIC microcontrollers. However, the midrange architectures are widely used. Our discussion will mainly confine to PIC16C74A whose architecture has most of the required features of a mid-range PIC microcontroller. Study of any other mid-range PIC microcontroller will not cause much variation from the basic architecture of PIC 16C74A ..

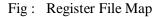

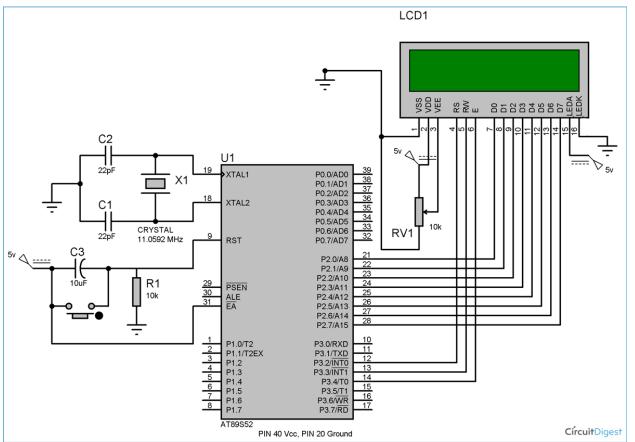

PIC 16C74A has 5 I/O Ports. Each port is a bidirectional I/O port. In addition, they have the following alternate functions.

| Port   | Altenative use  | s of I/O pins  | No.of I/O pins |

|--------|-----------------|----------------|----------------|

| Port A | A/D Converte    | r inputs       | 6              |

| Port B | External inter  | 8              |                |

| Port C | Serial port, Ti | 8              |                |

| Port D | Parallel slave  | 8              |                |

| Port E | A/D Converte    |                | 3              |

|        |                 | Total I/O pins | 33             |

|        |                 | Total pins     | 40             |

In addition to I/O pins, there is a Master clear pin (MCLR) which is equivalent to reset in 8051. However, unlike 8051, MCLR should be pulled low to reset the micro controller. Since PIC16C74Ahas inherent power-on reset, no special connection is required with MCLR pin to reset the micro controller on power-on.

There are two VDD pins and two VSS pins. There are two pins (OSC1 and OSC2) for connecting the crystal oscillator/ RC oscillator. Hence the total number of pins with a 16C74A is 33+7=40. This IC is commonly available in a dual-in-pin (DIP) package.

### (Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

Fig : Pin configuration of PIC 16C74A

# **Instruction Set of PIC Microcontroller**

### **Guidelines from Microchip Technology**

For writing assembly language program Microchip Technology has suggested the following guidelines.

- 1. Write instruction mnemonics in lower case. (e.g., movwf)

- 2. Write the special register names, RAM variable names and bit names in upper case. (e.g., PCL, RP0, etc.)

- 3. Write instructions and subroutine labels in mixed case. (e.g., Mainline, LoopTime)

### **Instruction Set:**

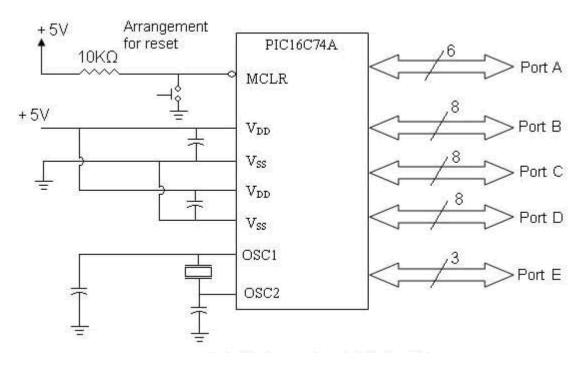

The instruction set for PIC16C74A consists of only 35 instructions. Some of these instructions are byte oriented instructions and some are bit oriented instructions.

The **byte oriented instructions** that require two parameters (For example, movf f, F(W)) expect the f to be replaced by the name of a special purpose register (e.g., PORTA) or the name of a RAM variable (e.g., NUM1), which serves as the source of the operand. 'f' stands for file register. The F(W) parameter is the destination of the result of the operation. It should be replaced by:

#### (Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

F, if the destination is to be the source register.

W, if the destination is to be the working register (i.e., Accumulator or W register).

The **bit oriented instructions** also expect parameters (e.g., btfsc f, b). Here 'f' is to be replaced by the name of a special purpose register or the name of a RAM variable. The 'b' parameter is to be replaced by a bit number ranging from 0 to 7.

For example:

Z equ 2 btfsc STATUS, Z

Z has been equated to 2. Here, the instruction will test the Z bit of the STATUS register and will skip the next instruction if Z bit is clear.

The **literal instructions** require an operand having a known value (e.g., 0AH) or a label that represents a known value.

For example:

| NUM equ 0AH ; | Assigns 0AH to the label NUM ( a constant |

|---------------|-------------------------------------------|

| ) movlw NUM ; | will move 0AH to the W register.          |

Every instruction fits in a single 14-bit word. In addition, every instruction also executes in a single cycle, unless it changes the content of the Program Counter. These features are due to the fact that PIC micro controller has been designed on the principles of RISC (Reduced Instruction Set Computer) architecture.

#### **Instruction set:**

| Mnemonics     | Description                                 | Instruction<br>Cycles |

|---------------|---------------------------------------------|-----------------------|

| bcf f, b      | Clear bit b of register f                   | 1                     |

| bsf f, b      | Set bit b of register f                     | 1                     |

| Clrw          | Clear working register W                    | 1                     |

| clrf f        | Clear f                                     | 1                     |

| movlw k       | Move literal 'k' to W                       | 1                     |

| movwf f       | Move W to f                                 | 1                     |

| movf f, F(W)  | Move f to F or W                            | 1                     |

| swapf f, F(W) | Swap nibbles of f, putting result in F or W | 1                     |

| andlw k       | And literal value into W                  | 1 |

|---------------|-------------------------------------------|---|

| andwf f, F(W) | And W with F and put the result in W or F | 1 |

| andwf f, F(W) | And W with F and put the result in W or F | 1 |

| iorlw k       | inclusive-OR literal value into W         | 1 |

# (Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

| iorwf f, F(W)  | inclusive-OR W with f and put the result in F or W                                         | 1     |

|----------------|--------------------------------------------------------------------------------------------|-------|

| xorlw k        | Exclusive-OR literal value into W                                                          | 1     |

| xorwf f, F(W)  | Exclusive-OR W with f and put the result in F or W                                         | 1     |

| addlw k        | Add the literal value to W and store the result in W                                       | 1     |

| addwf f, F(W)  | Add W to f and store the result in F or W                                                  | 1     |

| sublw k        | Subtract the literal value from W and store the result in W                                | 1     |

| subwf f, F(W)  | Subtract f from W and store the result in F or W                                           | 1     |

| rlf f, F(W)    | Copy f into F or W; rotate F or W left through the carry bit                               | 1     |

| rrf f, F(W)    | Copy f into F or W; rotate F or W right through the carry bit                              | 1     |

| btfsc f, b     | Test 'b' bit of the register f and skip the next instruction if bit is clear               | 1 / 2 |

| btfss f, b     | Test 'b' bit of the register f and skip the next instruction if bit is set                 | 1 / 2 |

| decfsz f, F(W) | Decrement f and copy the result to F or W; skip the next instruction if the result is zero | 1 / 2 |

| incfcz f, F(W) | Increment f and copy the result to F or W; skip the next instruction if the result is zero | 1 / 2 |

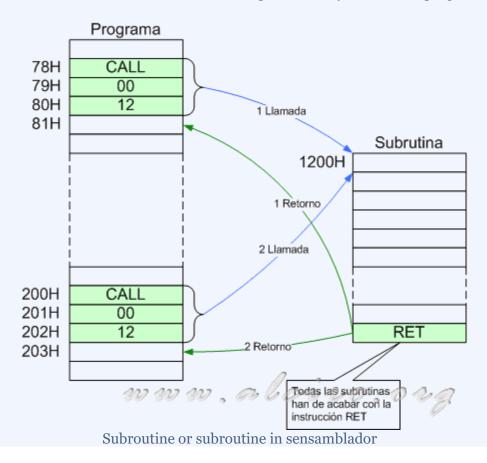

| goto label     | Go to the instruction with the label "label"                                               | 2     |

| call label     | Go to the subroutine "label", push the Program Counter in the stack                        | 2     |

| Retrun         | Return from the subroutine, POP the Program Counter from the stack                         | 2     |

| retlw k        | Retrun from the subroutine, POP the Program Counter from the stack; put k in W             | 2     |

| Retie          | Return from Interrupt Service Routine and re-enable interrupt                              | 2     |

| Clrwdt         | Clear Watch Dog Timer                                                                      | 1     |

| Sleep          | Go into sleep/ stand by mode                                                               | 1     |

| Nop            | No operation                                                                               | 1     |

### ( Prepared By: Mr. Ashok Saini , Assistant Professor , ECE)

### **Encoding of instruction:**

As has been discussed, each instruction is of 14-bit long. These 14-bits contain both op-code and the operand. Some examples of instruction encoding are shown here.

Example-1:

**bcf f, b** Clear 'b' bit of register 'f'

#### (Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

Operands:

$$0 \le f \le 127$$

$0 \le b \le 7$

Encoding:

The instruction is executed in one instruction cycle, i.e., 4 clock cycles. The activities in various clock cycles are as follows.

| <br>Q1 | Q2                   | Q3              | Q4                     |

|--------|----------------------|-----------------|------------------------|

| Decode | Read<br>register 'f' | Process<br>data | VVrite<br>register 'f' |

Example-2:

goto K Go to label 'k' instruction

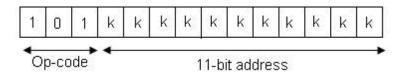

Operand:  $0 \le K \le 2047$  (11-bit address is specified) Operation: <10:0> PCLATH <4:3>  $\longrightarrow$  PC <12:11> Encoding:

$K \longrightarrow PC$

Since this instruction requires modification of program Counter, it takes two instruction cycles for execution.

Q-Cycle activities are shown as follows.

### ( Prepared By: Mr. Ashok Saini , Assistant Professor , ECE)

|                       | Q1               | Q2                  | Q3               | Q4               |  |

|-----------------------|------------------|---------------------|------------------|------------------|--|

| 1st instruction cycle | Decode           | Read<br>literal 'k' | Process<br>data  | Write<br>to PC   |  |

| 2nd Instruction cycle | No-<br>Operation | No-<br>Operation    | No-<br>Operation | No-<br>Operation |  |

# **Addressing Modes of pic microcontroller**

To know the working principal and data handling, we need to have clear knowledge on addressing modes of pic microcontroller. Now we can see that how we can categorise different addressing modes of pic microcontroller. In PIC micro controller, it having mainly five addressing modes. Those are

- 1. Immediate addressing mode

- 2. Register operand addressing mode

- 3. Memory operand addressing mode

- 4. Direct addressing

- 5. Indirect addressing.

# 1. Immediate addressing mode:

In this addressing mode, the operand is a number or constant not an address as **MOVLW 43h**, the operand here is data not address. So in this addressing mode of pic microcontroller data is directly transfer. And data is immediate after the opcode. That is why this type of addressing is called immediate addressing. This way is fast in execution.

# 2. Register operand addressing mode:

In this addressing mode, the operand is a Register which holds the data to be execute. Register operand addressing mode deals with the registers like: CLR W

# 3. Memory operand addressing mode :

In this addressing mode, the operand is an address of Memory location which holds the data to be execute. Again memory operand addressing mode is under two category

- A). Direct addressing like CLRF 13h. We deal with the address or the memory location.

- B). Indirect addressing. we use in it INDF and FSR registers.

- 4. Direct addressing:

Direct Addressing is done through a 9-bit address. This address is obtained by connecting 7th bit of direct address. By using an instruction with two bits (RP1, RP0) from STATUS register. this is shown on bellow Figure . Any access to SFR registers can be an example of direct addressing

(Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

# 5.Indirect addressing:

It does not take an address from an instruction. But it derives from IRP bit of STATUS and FSR registers. Addressed location is accessed through INDF register. And INDF register in fact holds the address indicated by the FSR. Indirect addressing is very convenient for manipulating data arrays located in GPR registers. In this case, it is necessary to initialise FSR register with a starting address of the array, and the rest of the data can be accessed by increment the FSR register. Figure shows the indirect addressing concept.

(Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

**Timer 2 Overview**

#### (Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

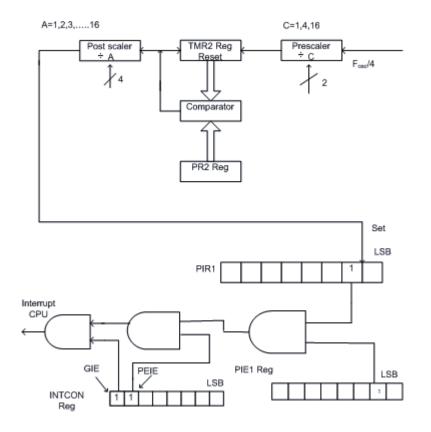

Fig : Schematic diagram showing operation of Timer 2

Timer 2 is an 8 - bit timer with a pre-scaler and a post-scaler. It can be used as the PWM time base for PWM mode of capture compare PWM (CCP) modules. The TMR2 register is readable and writable and is cleared on device reset.

The input clock (  $f_{osc}/4$ ) has a pre-scaler option of 1:1, 1:4 or 1:16 which is selected by bit 0 and bit 1 of T2CON register respectively.

The Timer 2 module has an 8bit period register (PR2). Timer-2 increments from 00H until it is equal to PR2 and then resets to 00H on the next clock cycle. PR2 is a readable and writable register. PR2 is initialised to FFH on reset.

The output of TMR2 goes through a 4bit post-scaler (1:1, 1:2, to 1:16) to generate a TMR2 interrupt by setting TMR2IF.

#### (Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

Fig: The T2CON Register

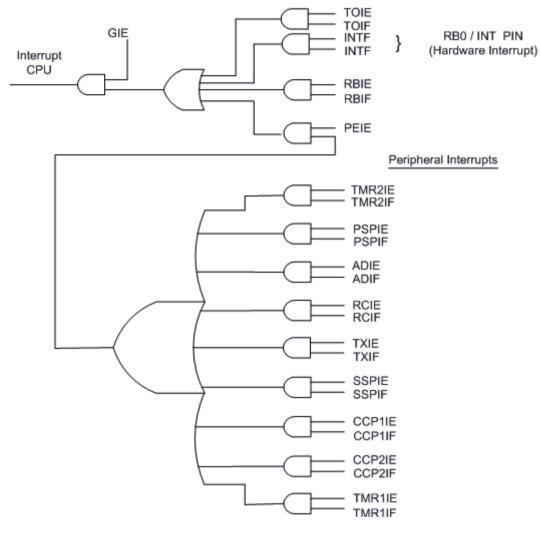

#### Interrupt Logic in PIC 16C74A

PIC 16C74A microcontroller has one vectored interrupt location (i.e., 0004H) but has 12 interrupt sources. There is no interrupt priority. Only one interrupt is served at a time. However interrupts can be masked. The interrupt logic is shown below :

### ( Prepared By: Mr. Ashok Saini , Assistant Professor , ECE)

Fig : Schematic diagram showing the interrupt logic for PIC

(Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

# TIMER 2 SCALAR INITALISATION:

Timer2 is an 8-bit timer with a prescaler, a postscaler, and a period register. Using the prescaler and postscaler at their maximum settings, the overflow time is the same as a 16-bit timer. Timer2 is the PWM time-base when the CCP module(s) is used in the PWM mode.

Figure shows a block diagram of Timer2. The postscaler counts the number of times that the TMR2 register matched the PR2 register. This can be useful in reducing the overhead of the interrupt service routine on the CPU performance.

#### Sets flag bit TMR2 (1) TMR2IF Prescaler TMR2 reg 1:1, 1:4, 1:16 Reset Fosc/4 Postscaler 1:1 Comparator to 1:16 ĒΟ 47 T2CKPS1:T2CKPS0 4 PR2 reg TOUTPS3:TOUTPS0 Note: TMR2 register output can be software selected by the SSP Module as a baud clock.

# Figure : Timer2 Block Diagram

# **Control Register:**

Register shows the Timer2 control register.

# **Register : T2CON: Timer2 Control Register**

|                  | —             | TOUTPS3                                        | TOUTPS2                    | TOUTPS1   | TOUTPS0    | TMR2ON    | T2CKPS1    | T2CKPS0 |

|------------------|---------------|------------------------------------------------|----------------------------|-----------|------------|-----------|------------|---------|

|                  | b-7           |                                                |                            |           |            |           |            | b-0     |

| bit 7<br>bit 6:3 | <b>T</b><br>0 | Unimpleme<br>TOUTPS3<br>000 = 1:1<br>001 = 1:2 | <b>:TOUTP</b><br>Postscale | S0: Timer | 2 Output I | Postscale | Select bit | Ś       |

#### (Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

|         | •                                                  |

|---------|----------------------------------------------------|

|         | •                                                  |

|         | •                                                  |

|         | 1111 = 1:16 Postscale                              |

| bit 2   | TMR2ON: Timer2 On bit                              |

|         | 1 = Timer2 is on                                   |

|         | 0 = Timer2 is off                                  |

| bit 1:0 | T2CKPS1:T2CKPS0: Timer2 Clock Prescale Select bits |

|         | 00 = Prescaler is 1                                |

|         | 01 = Prescaler is 4<br>1x = Prescaler is 16        |

|         | 1x - riescaler is 10                               |

| Logond |

|--------|

| Legend |

|        |

| R = Readable bit | W = Writable bit |

|------------------|------------------|

|                  |                  |

U = Unimplemented bit, read as '0'

- n = Value at POR reset

#### **Timer Clock Source**

The Timer2 module has one source of input clock, the device clock (Fosc/4). A prescale option of 1:1, 1:4 or 1:16 is software selected by control bits T2CKPS1:T2CKPS0 (T2CON<1:0>).

#### Timer (TMR2) and Period (PR2) Registers

The TMR2 register is readable and writable, and is cleared on all device resets. Timer2 incre- ments from 00h until it matches PR2 and then resets to 00h on the next increment cycle. PR2 is a readable and writable register.

TMR2 is cleared when a WDT, POR, MCLR, or a BOR reset occurs, while the PR2 register is set.

Timer2 can be shut off (disabled from incrementing) by clearing the TMR2ON control bit (T2CON<2>). This minimizes the power consumption of the module.

#### **TMR2 Match Output**

The match output of TMR2 goes to two sources:

- 1. Timer2 Postscaler

- 2. SSP Clock Input

There are four bits which select the postscaler. This allows the postscaler a 1:1 to 1:16 scaling (inclusive). After the postscaler overflows, the TMR2 interrupt flag bit (TMR2IF) is set to indicate the Timer2 overflow. This is useful in reducing the software overhead of the Timer2 interrupt ser- vice routine, since it will only execute once every postscaler # of matches.

The match output of TMR2 is also routed to the Synchronous Serial Port module, which may soft- ware select this as the clock source for the shift clock.

#### **Clearing the Timer2 Prescaler and Postscaler**

The prescaler and postscaler counters are cleared when any of the following occurs:

- · a write to the TMR2 register

- a write to the T2CON register

Note: When T2CON is written TMR2 does not clear.

any device reset (Power-on Reset, MCLR reset, Watchdog Timer Reset, Brown-out Reset, or Parity Error Reset)

#### (Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

During sleep, TMR2 will not increment. The prescaler will retain the last prescale count, ready for operation to resume after the device wakes from sleep.

(Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

# **Table : Registers Associated with Timer2**

| Name   | Bit 7                     | Bit 6                                                      | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1   | Bit 0   | Value on:<br>POR,<br>BOR, PER | Value on<br>all other<br>resets |

|--------|---------------------------|------------------------------------------------------------|---------|---------|---------|--------|---------|---------|-------------------------------|---------------------------------|

| INTCON | GIE                       | PEIE                                                       | TOIE    | INTE    | RBIE    | TOIF   | INTF    | RBIF    | 0000 000x                     | 0000 000u                       |

| PIR    | TMR2IF <sup>(1)</sup> 0 0 |                                                            |         |         |         |        |         |         |                               | 0                               |

| PIE    |                           | TMR2IE <sup>(1)</sup> 0 0                                  |         |         |         |        |         |         |                               |                                 |

| TMR2   | Timer                     | Timer2 module's register 0000 0000 0000 0000 0000 0000     |         |         |         |        |         |         |                               |                                 |

| T2CON  |                           | TOUTPS3                                                    | TOUTPS2 | TOUTPS1 | TOUTPS0 | TMR2ON | T2CKPS1 | T2CKPS0 | -000 0000                     | -000 0000                       |

| PR2    | Timer                     | Timer2 Period Register         1111 1111         1111 1111 |         |         |         |        |         |         |                               |                                 |

Legend: x = unknown, u = unchanged, - = unimplemented read as '0'.

Shaded cells are not used by the Timer2 module. Note 1: The position of this bit is device dependent.

# **INITIALISATION**

Example shows how to initialize the Timer2 module, including specifying the Timer2 prescaler and postscaler.

|                | CLRF         | T2CON                    | ;   | Stop Timer2, Prescaler = 1:1,            |

|----------------|--------------|--------------------------|-----|------------------------------------------|

|                |              |                          | ;   | Postscaler = 1:1                         |

|                | CLRF         | TMR2                     | ;   | Clear Timer2 register                    |

|                | CLRF         | INTCON                   | ;   | Disable interrupts                       |

|                | BSF          | STATUS, RP0              | ;   | Bank1                                    |

|                | CLRF         | PIE1                     | ;   | Disable peripheral interrupts            |

|                | BCF          | STATUS, RP0              | ;   | Bank0                                    |

|                | CLRF         | PIR1                     | ;   | Clear peripheral interrupts Flags        |

|                | MOVL<br>W    | 0x72                     | ;   | Postscaler = $1:15$ , Prescaler = $1:16$ |

|                | MOVW<br>F    | T2CON                    | ;   | Timer2 is off                            |

|                | BSF          | T2CON, TMR2ON            | ;   | Timer2 starts to increment               |

| ;<br>• The Tin | er? interru  | pt is disabled, do poll  | inc | on the overflow hit                      |

|                | ierz miterre | ipt is disubled, do poli |     | , on the overnow on                      |

| ,<br>T2_OVF    | L_WAIT       |                          |     |                                          |

|                | BTFSS I      | PIR1, TMR2IF             | ;   | Has TMR2 interrupt occurred? GOTO        |

|                |              | T2_OVFL_WAIT             | ;   | NO, continue loop                        |

| ;              |              |                          |     |                                          |

| ; Timer h      | as overflov  | ved                      |     |                                          |

| ;              | BCF          | PIR1, TMR2IF             | ;   | YES, clear flag and continue.            |

# **INTSERVICE INTERRUPT SERVICE ROUTINE:**

- Whenever an interrupt occur, the CPU automatically pushes the return address in the PC onto the stack and clear the GIE (global interrupt enable) bit, disabling further interrupts. No other registers, or **W**, are automatically set aside.

- The first job of Intservice is to set aside the content of **W** and of **STATUS**. Then they can be restored at the end of the ISR to exactly the same state they were in when the interrupt occurred, as required for the proper execution of the machine code.

(Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

Once interrupt have been enabled , Bank 1 register and RAM should only be accessed by indirect addressing

| IntService                                                             |           |                       |                                           |  |  |  |  |  |  |

|------------------------------------------------------------------------|-----------|-----------------------|-------------------------------------------|--|--|--|--|--|--|

| ; set asude W and STATUS                                               |           |                       |                                           |  |  |  |  |  |  |

|                                                                        | movwf     | W_TEMP                | ;copy W to RAM                            |  |  |  |  |  |  |

|                                                                        | swapf     | STATUS,W              | ;move STATUS to W without affecting Z bit |  |  |  |  |  |  |

|                                                                        | movwf     | STATUS_TEMP           | ;copy to RAM                              |  |  |  |  |  |  |

| ; execute polling routine                                              |           |                       |                                           |  |  |  |  |  |  |

|                                                                        | btfsc     | P1R1,TMR21F           | ;check for timer2 interrupt               |  |  |  |  |  |  |

|                                                                        | call      | TIMER2                | ; if ready, service it                    |  |  |  |  |  |  |

| ;                                                                      | btfsc     |                       | ; check another interrupt source          |  |  |  |  |  |  |

| ;                                                                      | call      |                       | ; if ready, service it                    |  |  |  |  |  |  |

| ;                                                                      | btfsc     |                       | ; check another interrupt source          |  |  |  |  |  |  |

| ;                                                                      | call      |                       | ; if ready, service it                    |  |  |  |  |  |  |

|                                                                        |           |                       |                                           |  |  |  |  |  |  |

| ; restore STATUS                                                       | S and W a | nd retirn from interr | upt                                       |  |  |  |  |  |  |

|                                                                        | swapf     | STATUS_TEMP,          | W ; Restore STATUS bits                   |  |  |  |  |  |  |

|                                                                        | movwf     | STATUS                | ;without affecting z bit                  |  |  |  |  |  |  |

|                                                                        | swapf     | W_TEMP,F              | ; swap W_TEMP                             |  |  |  |  |  |  |

|                                                                        | swapf     | W_TEMP,W              | -                                         |  |  |  |  |  |  |

|                                                                        |           |                       |                                           |  |  |  |  |  |  |

| ;;;;;;;;;;;;;;;;;TIMER2 SUBROUTINE;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;;; |           |                       |                                           |  |  |  |  |  |  |

| т: о                                                                   |           |                       |                                           |  |  |  |  |  |  |

| Timer2                                                                 | 1 6       |                       |                                           |  |  |  |  |  |  |

|                                                                        | bcf       | PIR1,TMR2IF           | ; Clear interrupt flag (bank 0)           |  |  |  |  |  |  |

|                                                                        | decf      | SCALEWR,F             |                                           |  |  |  |  |  |  |

|                                                                        | return    |                       |                                           |  |  |  |  |  |  |

The central code of **IntService** is a sequence of **btfsc**, **cal**l instruction pairs. If tested flag is set, ISR is called otherwise call is skipped. This sequence is called polling subroutine.

# **LOOPTIME SUBROUTINE:**

- **LoopTime** subroutine that is called within mainline loop is able to make the time around the loop take exactly 10 ms. For the loop time work correctly, the worst-case (i.e. longest) execution of the remainder of the code in the main loop plus the worst-case execution time for all the ISR that could request service within a 10-ms interval must be less than 10-ms.

- The mainline overrun condition is easily avoided for many, if not most, applications. If it is not avoided during one loop, the next looptime will be shortened to compensate.

- On the other hand, even if this mainline overrun condition does not occur, the long range timing provided by the loop time subroutine will still be accurate as long as no counts of SCALAR are

#### (Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

ever lost.

LoopTime

btfssSCALER, 7gotoLoopTimemovlw5addwfSCALAR, Freturn

IntService, which in turn wait on successive interrupt from timer2. When the timer2 interrupt occurs that finally decrements SCALER down from H'00' to H'FF', the goto Loop Time instruction will be skipped, five will be added to SCALER (resulting in SCALER =4), and the CPU will return from the ISR.

# **UART:**

An universal asynchronous receiver and transmitter (UART) is an integrated circuit which is programmed to control a computer's interface to its attached serial devices [3]. Specifically, it provides the system with the RS-232C Data Terminal Equipment (DTE) interface, enabling it to talk to and exchange data with modems and some other serial devices. Being a part of this interface, the UART also provides the basic operations as:

- Converts the bytes it gets from the computer along parallel circuits to a single serial bit stream for outbound transmission.

- For inbound transmission, converts the serial bit stream to the bytes that the system handles.

- Adds a parity bit after selection in outbound transmissions, checks the parity of incoming bytes (if selected) and rejects the parity bit.

- Adds start and stop delineators for outbound and helps to strip them from inbound transmissions.

- Handles interrupts from keyboard and mouse (which are serial devices with special ports).

####

Serial Data Transmission

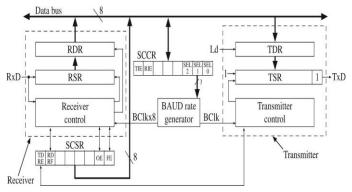

#### I. UART DESIGN:

The UART block diagram consists of three main components, *Transmitter control, Receiver control and Baud rate generator*. When transmitting, the UART takes eight bits of parallel data, converts the data to a serial bit stream that has a start bit (logic '0'), 8 data bits, and a stop bit (logic '1'). When receiving, the UART initially detects a start bit, then receives a stream of 8 data bits and

#### ( Prepared By: Mr. Ashok Saini , Assistant Professor , ECE)

translates the data into parallel when it detects the stop bit. As no clock is transmitted, the UART must synchronize incoming stream of bits with the local clock.

The following six 8bit registers are used.

1- RSR- Receive shift register.

2- RDR- Receive data register.

3- TDR- Transmit data register.

4- TSR- Transmit shift register.

5-SCCR- Serial communications control register.

6-SCSR- Serial communications status registers.

Assume that the UART is connected to a microcontroller data and address bus so that the CPU can read and write to the registers. RDR, TDR, SCCR and SCSR are memory mapped. RDR, SCSR, SCCR can drive the data bus through tristate buffers.TDR and SCCR can be loaded from the data bus.

Besides the registers, the three main components of the UART are the Baud rate generator, the receiver and transmitter control. The Baud rate generator divides the clock of the system down to provide the bit clock (bclk) with a period equal to one bit time and also bclkx8, which has a frequency eight times the bclk frequency. The TDRE (transmit data register empty) bit in the SCSR is set when TDR is empty.

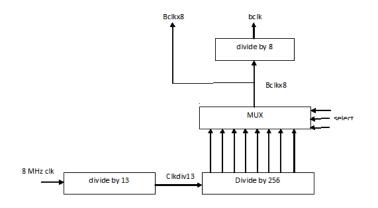

## A. Baudrate Generator

The 8 MHz clock system clock is first divided by 13 using a counter. This counter output goes to 8 bit binary counter. The output from the flip-flops in this counter relates to divide by 2, 4 and so on upto divide by 256. Out of these outputs, one is selected by a multiplexer. The multiplexer selects inputs that come from the lower 3bits of the sccr. The output corresponds to bclkx8, which is again divided by 8 to give bclk.

Fig. UART design model block diagram

Initially the process increments the divide by 13 counters on the rising edge of the system clock. The second process increments the divide by 256 counters on the rising edge of clkdiv13. A concurrent statement generates the mux output, bclkx8. The third process increments the divide by 8 counters on the rising edge of bclkx8 to generate bclk.

(Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

Fig. Baud rate generator block diagram.

#### **B.** UART Transmitter

When the microcontroller is ready to transmit data, the following occurs.

- 1. The microcontroller waits until TDRE='1' [5] and then loads a byte of data into TDR clears TDRE.

- 2. UART transfers data from TDR to TSR and sets TDRE.

- 3. The UART provides an output as a start bit '0' for one bit time and then shifts TSR right to transmit the eight data bits followed by the stop bit '1'.

- 4. In this step the UART transfers data from TDR to TSR and sets TDRE.

- 5. The UART gives a output as a start bit '0' for one bit time and shifts TSR right to transmit the eight data bits followed by the stop bit '1'.

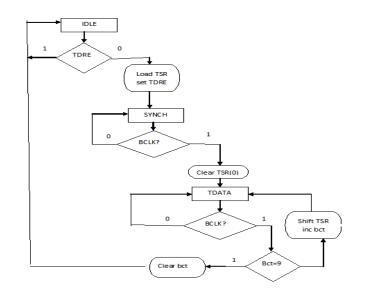

### SM chart of transmitter

In the IDLE state, the SM waits until TDR is loaded and consequently TDRE is cleared. In SYNCH state, the SM waits for the rising edge of the bit clock and then clears the low order bit of the TSR to transmit a '0' for one bit time. In the TDATA state, each time bclk↑ is detected, TSR is shifted right to transmit the next data bit and the bit counter (bct) is incremented. When bct=9 eight data bits and a stop bit have been transmitted, bct is then cleared and the SM goes back to idle.

The transmitter contains the TDR and TSR registers and the transmit control. It interfaces with TDRE and data bus (DBUS). The first process represents the combinational network, which generates the next state and control signals. The second process updates the registers on the rising edge of the clock. The signal bclk\_rising is '1' for one system clock time following the rising edge of bclk. To generate bclk\_rising, bclk is stored in a flip-flop named bclk\_dlayed. Then bclk\_rising is '1' if the current value of bclk is '1' and the previous value is '0'.

(Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

Fig. SM chart of transmitter

## C. UART Receiver

- 1. When UART detects a start bit, it reads the left over bits serially and shifts them into RSR.

- 2. When all the data bits and the stop bit are received, the RSR loads into RDR and the flag of Receive Data Register Full (RDRF) in the SCSR is set.

- 3. The microcontroller checks for the RDRF flag, and if it is set, the flag is cleared by reading RDR.

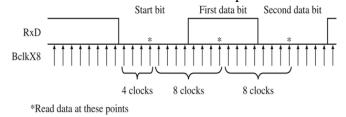

RxD is sampled eight times during each bit time. It is sampled on the rising edge of the BClkX8. The bit is read in middle of each bit time for maximum reliability. When RxD first goes low, we will wait for four BClkX8 periods, which should take us closer to the middle of the first data bit. Then reading once per eight BClkX8 clocks is continued until we have read the stop bit.

Fig. Sampling RxD with Bclkx8

## SM chart of receiver

Two counters are used ct1 counts the number of BClkX8 clocks. ct2 counts the number of bits received after the start bit is encountered. In the IDLE state, the SM waits for the start bit (RxD = '0') and then goes to start detected state. Now the SM waits for the rising edge of BClkX8 and samples RxD once more. Since the start bit should be '0' for eight BClkX8 clocks, a '0' should be read. As ct1 is still 0, it is incremented and SM waits for the rising edge of BClkX8.If RxD = '1', this is an error

## (Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

condition and SM clears ct1 and resets to the IDLE state. Otherwise SM keeps looping till RxD is '0'. When RxD is '0' for the fourth time, ct1 = 3, so ct1 is cleared the state goes to receive data. In this state, the SM increments ct1 after every rising edge of BClkX8. After the eighth clock, ct1 = 7 and ct2 is checked. If it is not 8, the current value of RxD is shifted to RSR, ct2 is incremented, and ct1 is cleared. If ct2 = 8, all the 8 bits have been read and we should be at the middle of the stop bit. If RDRF = 1,the microcontroller has not yet read the previously received data byte, and an overrun error has occurred, where the OE flag in the status register is set and the new data is ignored. If RxD = '0', the stop bit has not been detected properly, and the framing error (FE) flag in the status register is set. If no errors have occurred, RDR is loaded from RSR. In all cases, RDRF is set to indicate that receive operation is completed and counter is cleared.

(Prepared By: Mr. Ashok Saini, Assistant Professor, ECE)

# <u>UNIT-3</u>

## 8051 Microcontroller Assembly Language Programming

#### What is a Programming Language?

Programming in the sense of Microcontrollers (or any computer) means writing a sequence of instructions that are executed by the processor in a particular order to perform a predefined task. Programming also involves debugging and troubleshooting of instructions and instruction sequence to make sure that the desired task is performed.

Like any language, Programming Languages have certain words, grammar and rules. There are three types or levels of Programming Languages for 8051 Microcontroller. These levels are based on how closely the statements in the language resemble the operations or tasks performed by the Microcontroller.

The three levels of Programming Languages are:

- Machine Language

- Assembly Language

- High-level Language

#### Machine language

In Machine language or Machine Code, the instructions are written in binary bit patterns i.e. combination of binary digits 1 and 0, which are stored as HIGH and LOW Voltage Levels. This is the lowest level of programming languages and is the language that a Microcontroller or Microprocessor actually understands.

## **Assembly Language**

The next level of Programming Language is the Assembly Language. Since Machine Language or Code involves all the instructions in 1's and 0's, it is very difficult for humans to program using it.

Assembly Language is a pseudo-English representation of the Machine Language. The 8051 Microcontroller Assembly Language is a combination of English like words called Mnemonics and Hexadecimal codes.

It is also a low level language and requires extensive understanding of the architecture of the Microcontroller.

### **High-level Language**

The name High-level language means that you need not worry about the architecture or other internal details of a microcontroller and they use words and statements that are easily understood by humans.

Few examples of High-level Languages are BASIC, C Pascal, C++ and Java. A program called Compiler will convert the Programs written in High-level languages to Machine Code.

### Why Assembly Language?

Although High-level languages are easy to work with, the following reasons point out the

## ( Prepared By: Mr. Ashok Saini , Assistant Professor , ECE)

advantage of Assembly Language

- The Programs written in Assembly gets executed faster and they occupy less memory.

- With the help of Assembly Language, you can directly exploit all the features of a Microcontroller.

- Using Assembly Language, you can have direct and accurate control of all the Microcontroller's resources like I/O Ports, RAM, SFRs, etc.

- Compared to High-level Languages, Assembly Language has less rules and restrictions.

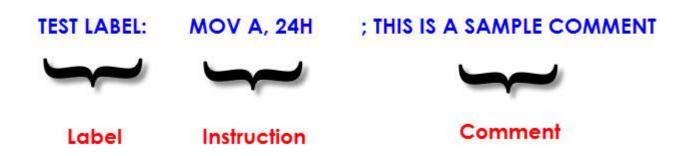

## Structure of the 8051 Microcontroller Assembly Language

Instructions

The Structure or Syntax of the 8051 Microcontroller Assembly Language is discussed here. Each line or statement of the assembly language program of 8051 Microcontroller consists of three fields: Label, Instruction and Comments.

The arrangement of these fields or the order in which they appear is shown below.

[Label:]

[//Comments]

Before seeing about these three fields, let us first see an example of how a typical statement or line in an 8051 Microcontroller Assembly Language looks like.

## TESTLABEL: MOV A, 24H ; THIS IS A SAMPLE COMMENT

In the above statement, the "TESTLABEL" is the name of the Label, "MOV A, 24H" is the Instruction and the "THIS IS A SAMPLE COMMENT" is a Comment.

## Label

The Label is programmer chosen name for a Memory Location or a statement in a program. The Label part of the statement is optional and if present, the Label must be terminated with a Colon (:).

( Prepared By: Mr. Ashok Saini , Assistant Professor , ECE)

An important point to remember while selecting a name for the Label is that they should reduce the need for documentation.

## Instruction

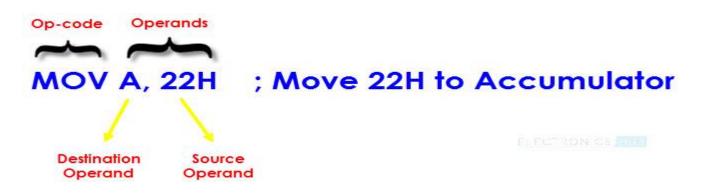

The Instruction is the main part of the 8051 Microcontroller Assembly Language Programming as it is responsible for the task performed by the Microcontroller. Any Instruction in the Assembly Language consists of two parts: Op-code and Operand(s).

The first part of the Instruction is the Op-code, which is short for Operation Code, specifies the operation to be performed by the Microcontroller. Op-codes in Assembly Language are called as Mnemonics. Op-codes are in binary format (used in Machine Language) while the Mnemonic (which are equivalent to Op-codes) are English like statements.

The second part of the instruction is called the Operand(s) and it represents the Data on which the operation is performed. There are two types of Operands: the Source Operand and the Destination Operand. The Source Operand is the Input of the operation and the Destination Operand is where the result is stored.

## **Comments**

The last part of the Structure of 8051 Assembly Language is the Comments. Comments are statements included by the developer for easier understanding of the code and is used for proper documentation of the Program.

Comments are optional and if used, they must begin with a semicolon (;) or double slash (//) depending on the Assembler.

The following statements will show a few possible ways of using Label, Instruction and Comments.

Label without instruction and comment: LABEL:

Line with Label and Instruction: LABEL: MOV A, 22H

( Prepared By: Mr. Ashok Saini , Assistant Professor , ECE)

Line with Instruction and Comment:

MOV A, 22H ; THIS IS A COMMENT

# **8051 Microcontroller Assembly Language Directives**

Assembly Language Directives are not the instructions to the 8051 Microcontroller Assembler even though they are written in the Mnemonic field of the program. Assembly Language Directives are actually instructions to the Assembler and directs the Assembler Program what to do during the process of Assembling.

The Assembly Language Directives do not have any effect on the contents of the 8051 Microcontroller Memory (except DB and DW directives).

These Directives are dependent on the Assembler Program and in case of ASM51 Assembler, the following are the categories of Directives.

| Assembler State Control | ORG, END, USING                                  |

|-------------------------|--------------------------------------------------|

| Symbol Definition       | SEGMENT, EQU, SET, DATA, IDATA, XDATA, BIT, CODE |

| Storage Initialization  | DS, DBIT, DB, DW                                 |

| Program Linkage         | PUBLIC, EXTERN, NAME                             |

| Segment Selection       | RSEG, CSEG, DSEG, ISEG, BSEG, XSEG               |

We will now see about few of the important and frequently used Assembly Language Directives.

## ORG – Set Origin

The 8051 Microcontroller Assembly Language Program will start assembling from the Program Memory Address 0000H. This is also the address from which the 8051 Microcontroller will start executing the code.

## ( Prepared By: Mr. Ashok Saini , Assistant Professor , ECE)

In order place the Program and Data anywhere in the Address Space of the 8051 Microcontroller, you can use the ORG Directive.

## Examples

| ORG 0000H | ; Tells the Assembler to assemble the next statement at 0000H |

|-----------|---------------------------------------------------------------|

| LJMP MAIN | ; Code Memory at 0000H. Jump to MAIN.                         |

| ORG 000BH | ; Tells the Assembler to assemble the next statement at 000BH |

| MAIN: NOP | ; Code Memory at 000BH. MAIN starts here.                     |

|           |                                                               |

## DB – Define Byte